更多资料请访问 www.liruan.net

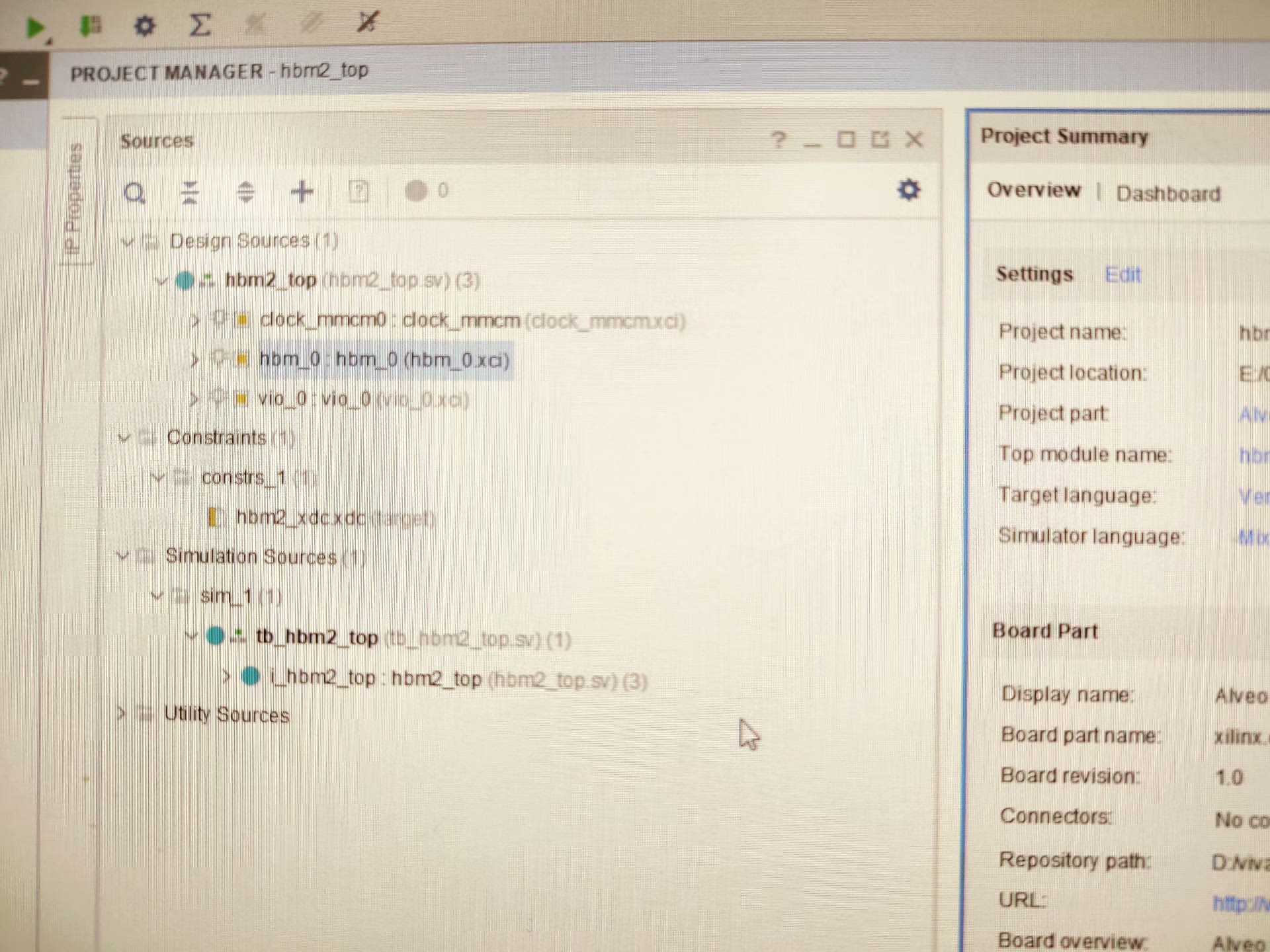

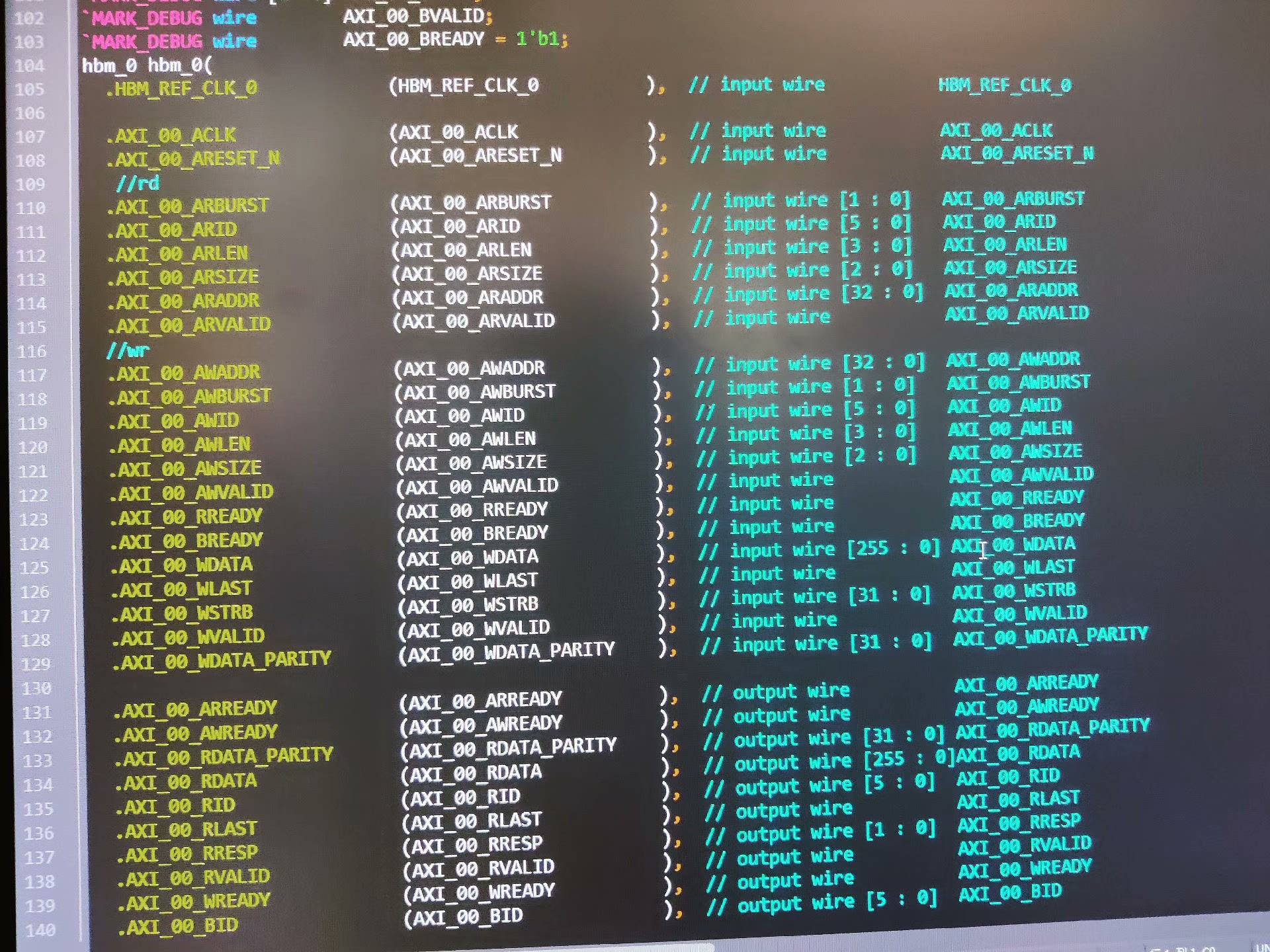

基于Fpga的hbm2系统设计:

实现对hbm2 ip核的读写访问接口时序控制。

HBM 器件可提供高达 820GB/s 的吞吐量性能和 32GB 的 HBM 容量,与 DDR5 实现方案相比,存储器带宽提高了 8 倍、功耗降低了 63%。

本工程提供了对hbm2 ip核的读写控制,方便开发人员、学习人员快速了解hbm2使用方法和架构设计。

工程通过vivado实现,并提供相应的。

【联系 微信shujuqudong1或shujuqudong6 QQ68823886或QQ27699885】

YID:44200713295440630